# **Metrology for Advanced Transistor and Memristor Devices and Materials**

Alain C. Diebold\* and Nathaniel C. Cady

College of Nanoscale Science and Engineering, SUNY Polytechnic Institute, 257 Fuller Rd., Albany, NY 12203

\* Correspondence should be addressed to: adiebold@sunypoly.edu

### **ABSTRACT**

As scaling becomes more challenging, new approaches to transistor design, new materials, and new devices are all being explored. Advanced transistor designs such as vertically stacked nanowire and nanosheet FETs (NW/NS FETs) provide a pathway to sub-10 nm devices. Ferroelectric High K enables extension of FinFET and NW/NS FETs as well as providing a potential dielectric for memristive devices, including RRAM and ferroelectric tunnel junctions. NW/NS FETs provide a significant challenge for both processing and process control due to the geometries associated with their 3D structure. Increasing computational power will ultimately require more than scaling, however. Neuromorphic (brain like) computing and non-Von Neumann computing architectures are now being explored as alternative options for increasing computation capability. To develop efficient neuromorphic and non-Von Neumann hardware, new devices and materials integration strategies are required. This paper provides an overview of advanced NW/NS transistors and new memristor devices and materials and their characterization and metrology.

Keywords: MMSE, scatterometry, Nanowire FETs, Nanosheet FETs, optical metrology

## 1. INTRODUCTION

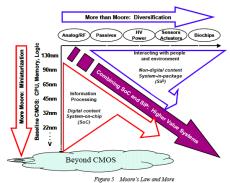

As the cost and challenges of further scaling to new technology nodes continue to increase, alternate means of increasing computational capability assume greater urgency. Evidence of this are the "More than Moore" approaches that have been the subject of semiconductor industry road mapping for more than ten years as shown Figure 1 from the International Roadmap for Devices and Structures.(1) New transistor structures that enable increased device packing density, new materials, and new devices are all critical means of achieving this goal. Here we discuss vertically stacked NW and NS FETs, ferroelectric High K, and new memristive memory device with emphasis on their metrology.

Figure 1. An overview of *More than Moore* approaches to increasing computational capability. Figure from the International Roadmap for Devices and Structures, https://irds.ieee.org/

Vertically stacked nanowire and nanosheet FETs (NW/NS FETs) provide a pathway to sub-10 nm devices by stacking transistor channels instead of spreading them horizontally as is done in planar multi-gate FETs.(2-7) This device design

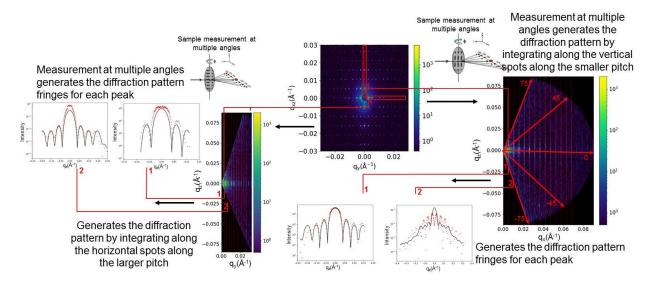

increases the challenges associated with measuring decrease feature dimensions.(2-7) NW and NS FET cross-sections are shown in Figure 2. Here, we present two methods that have been used for measuring NW/NS FET structures: Mueller Matrix Spectroscopic Ellipsometry based Scatterometry MMSE-scatterometry and Critical Dimension – Small Angle X-Ray Scattering (CD-SAXS). MMSE-scatterometry is sensitive to cross-polarized light scattering which enables measurement of challenging features including subsurface cavities.(8) Next, Critical Dimension Small Angle X-Ray Scattering (CD-SAXS) is described.(9) The diffraction information obtained by CD-SAXS also provides a means of characterizing subsurface 3D structures critical to these future transistor designs. Examples of characterization capability will include simulations of representative structures as well as experimental measurements of nanowire test structures used to develop etch processes (10).

Increasing computational power will ultimately require more than scaling, however. Neuromorphic (brain like) computing and non-Von Neumann computing architectures are now being explored as alternative options for increasing computation capability.(11) To develop efficient neuromorphic and non-Von Neumann hardware, new devices and materials integration strategies are required. Here we present memristor circuits being fabricated using High K materials, including ferroelectric High K and transition metal oxide resistive random access memory (RRAM). Ferroelectric High K is actively being pursued as a replacement for High K. The negative (differential) capacitance can reduce the voltage required for transistor switching and the dissipated current.(12) This is useful for both 14 nm node transistors and sub 10 nm transistor nodes (12, 13). Ferroelectric High K can also be used in memristor devices (13). Here we discuss the challenges associated with characterizing the crystal phase of these materials. Due to the nanoscale dimensions of the film, synchrotron based X-ray diffraction and extended X-ray absorption fine structure are being used to determine the phases present in these films. We also describe electrical characterization of these films in the context of memristive devices (primarily RRAM, FeRAM and FTJs). These circuits are being designed to mimic the function of synapses in the highly interconnected neuron pathways of the brain. The electrical switching behavior will be shown and with a high-level view of the electrical signals that are used to mimic brain-like behavior (11).

# 2. Mueller Matrix Spectroscopic Ellipsometry (MMSE) Scatterometry of Nanowire (NW)/Nanosheet (NS) Transistor Structures

Scatterometry is a well-established means of critical dimension measurement. When compared to traditional spectroscopic ellipsometry, MMSE scatterometry increases the ability to measure the 3D profiles of complicated 3D structures. The increased ability of MMSE scatterometry is due to the inclusion of all aspects of light scattering including cross-polarized scattering and depolarization.(8) Furthermore, MMSE provides 16 spectroscopic pieces of information (Mueller matrix elements) vs the two (Psi and Delta) provided by traditional SE which is a key advantage as it provides more structural information about the sample.(8) Here we apply MMSE scatterometry to the characterization of NW/NS test structures used to develop the etch processes used for fabrication of NW/NS FETS. The science and technology of MMSE scatterometry has been previously discussed in the literature and will not be repeated here. (8, 10)

Figure 2. Vertically Stacked Nanowire FET on the left and Nanosheet FET on the left. Figures adapted from references 14 and 15 and copyright IEEE.

Proc. of SPIE Vol. 11325 1132502-2

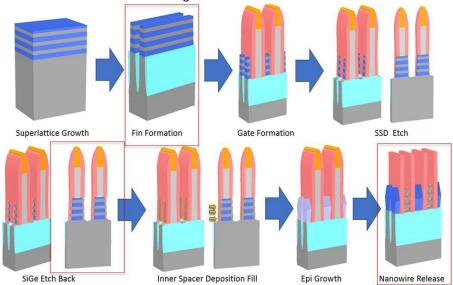

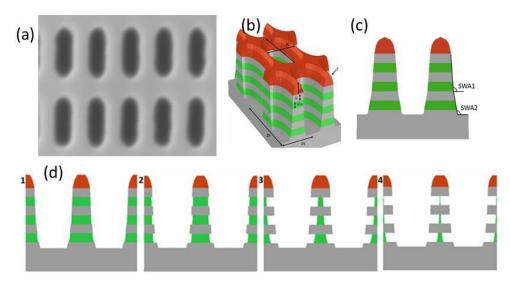

Process control for the fabrication of Gate-All-Around (GAA) NW/NS FETs from Si/SiGe/.../Si fins requires measurement of a number of structures that challenge metrology methods. The process flow for NW/NS FETs is shown in Figure 3. Key process steps include the release of the NW/NS channel and the deposition of the High K and metal gate layers. Nanowire test structures are used to develop the selective SiGe etch process used to release the channels, and are shown in Figure 4. Here, we discuss the use of MMSE-scatterometry and CD-SAXS to measure the extent of the selective etch. The results of the MMSE-scatterometry characterization of the selective etch process are shown in Figure 4(d) and for the CD-SAXS characterization in Figures 5 and 6.

Figure 3. The process flow for fabrication of GAA NW/NS FET. Figure copyright AIP and first published in Ref. 7.

Figure 4. The NWTS and the selective etch of subsurface SiGe layers is shown. A top down view of the holes in the test structure is shown in (a). A section of the optical structure model used for scatterometry simulations is shown in (b). A cross-section along the narrow part of the hole structure is shown in (c). The selective etch of the SiGe subsurface layers is shown in (d). The structures shown in (d) represent a cross-sectional view of the optimized optical model for the selectively etched structures. The amount of selective etch is (1)3.4nm, (2)10.5nm, (3)18.9nm and (4)21.9nm from the sidewall. Figure adapted from Reference 16 with copyright AIP and used with the authors' permission.

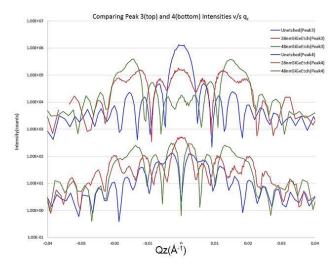

Figure 5. CD-SAXS characterization of the NWTS samples is described. Figure courtesy M. Korde, R.J. Kline, and D. Sunday.

Figure 6. CD-SAXS data showing the sensitivity to selective etching of SiGe layers in the NWTS. The dark blue diffraction data is from the unetched NWTS. The red diffraction data is from the sample having  $\sim 11$  nm etch from the sidewall, and the green diffraction data is from the sample having  $\sim 22$  nm of selective etching from the sidewall.

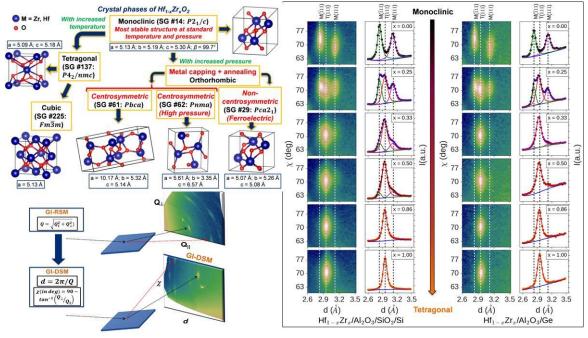

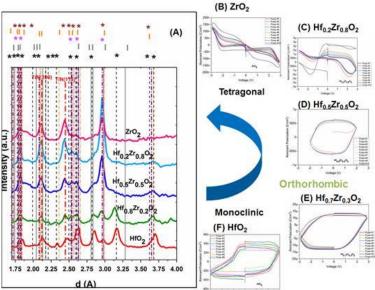

In addition to reduction in transistor feature dimension and new transistor designs, High K materials continue to advance. The drive to reduce the equivalent oxide thickness resulted in a transition to amorphous hafnium oxide based High K films. This was followed by the use of crystalline higher K hafnium oxide based which included HfZr oxides. The dielectric constant vs crystal phase for Hf oxide is 16 (monoclinic), 29 (cubic), and 70 (tetragonal). Similar trends are observed for HfZr oxide thus driving the need to find processes that resulted in stable higher K phases for the entire gate stack including metal gate. Subsequently, the need to reduce equivalent oxide thickness pushed the use of ferroelectric materials.(12, 13) Ferroelectric dielectric layers such as HfZr oxide provide a negative differential capacitance that reduces transistor operating voltage and power use. (12, 13) Stable fabrication of High K films requires metrology that is capable of determining the crystal phase. Characterization of the crystal phase of the high

Kcontinues to be challenging, especially in-line measurements. Previously, we have shown that synchrotron based grazing incidence in-plane X-Ray diffraction measurement methods can be used to determine the crystal phase as shown in Figure 7.(17) This methodology has been applied to ferroelectric HfZr oxide. In this case, the presence of the ferroelectric phase of HfZr oxide was verified by electrical characterization.(18)

Figure 7. The various crystal phases of HfZr oxide are shown in the upper left. A comparison of GI-I-XRD data in reciprocal space vs d spacing is shown in the lower left. A comparison of the change in crystal phase of  $Hf_{1-x}Zr_x$  oxide with Zr concentration x for silicon and germanium substrates is shown on the right. Figure copyright AIP and first published in Reference 17.

Figure 8. Correlation between crystal phase and electrical characterization of ferroeletric behavior. Figure copyright MRS and first published in Reference 18.

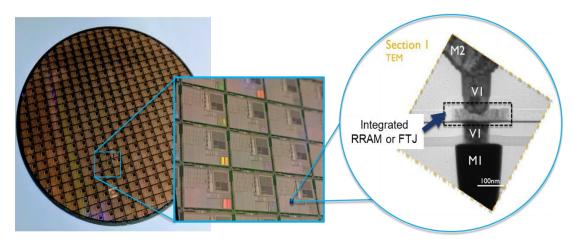

New devices and architectures are also providing challenges to metrology. Since the frequent exchange of information between memory and microprocessor slows overall computation, the need to keep information in the processing unit and have new approaches to memory is driving approaches such as neuromorphic computing based on memristive devices. Memristive devices can be fabricated using traditional silicon processes as shown in Figure 9. Work at SUNY Polytechnic Institute has demonstrated the integration of transition metal oxide based memristors in the first metallization layers of a 65nm CMOS process. (19, 20) To date, both  $HfO_2$  RRAM elements and  $Hf_{1-x}Zr_x$  ferroelectric tunnel junction (FTJ) structures have been integrated, specifically at the metal 1 (M1) / via 1 (V1) interface.

Figure 9. 300mm wafer-scale integration of memristive devices with CMOS. Memristors (including RRAM and/or FTJ) have been integrated at the metal 1 / via 1 interface in a standard 65nm CMOS process.

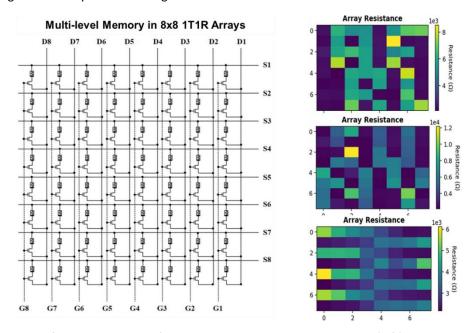

To demonstrate new architectures, arrays of 1 transistor 1 RRAM (1T1R) elements have been fabricated and tested for multi-bit data storage and so-called "in memory computing". An example of such an array and a visualization of multi-bit memory storage in the array is shown in Figure 10.

Figure 10. A schematic of an 8x8 1T1R array fabricated at SUNY Polytechnic Institute (left) and a visualization of multibit memory storage within that array (right).

## 5. ACKNOWLEDGEMENTS

A.C. Diebold acknowledges funding from SRC GRC and TEL Technology Center USA. We are thankful to Raja Muthinti from IBM and Nick Keller and Andy Antonelli from Nanometrics Inc. (now ONTO) for the help with scatterometry modeling and analysis. We would also like to acknowledge the support and guidance as well as the samples provided by TEL, Technology Center, USA and the collaboration for MMSE-scatterometry from Aelan Mosden, Subhadeep Kal and Cheryl Pereira and for High K and ferroelectric High K from Steve Consiglio, Kanda Tapily, Dina Triyoso, and Gert Leusink. ACD also gratefully acknowledges the collaboration and support provided graduate student Madhulika Korde for the CD-SAXS characterization of the NWTSs. N.C. Cady acknowledges funding from SRC and the Air Force Research labs and contributions from Karsten Beckmann, Sarah Rafiq, Maximilian Liehr, and Jubin Hazra.

### **REFERENCES:**

- 1. International Roadmap for Devices and Structures, https://irds.ieee.org/

- 2. Pan C, Member S, Raghavan P, et al. Technology / System Codesign and Benchmarking for Lateral and Vertical GAA Nanowire FETs at 5-nm Technology Node. 2015:1-8.

- 3. Sinha S, Yeric G, Chandra V, Cline B, Cao Y. Exploring Sub-20nm FinFET Design with Predictive Technology Models. 2012:283-288.

- 4. Han M, Chang C, Fellow L, Chen H, Cheng Y. Device and Circuit Performance Estimation of Junctionless Bulk FinFETs. 2013;60(6):1807-1813.

- 5. Singh N, Agarwal A, Bera LK, et al. High-Performance Fully Depleted Silicon Nanowire (Diameter ≤ 5 nm ) Gate-All-Around CMOS Devices. 2006;27(5):383-386.

- 6. Park J. Multiple-Gate SOI MOSFETs: 2013;(August). doi:10.1109/TED.2002.805634

- 7. Kuhn KJ, Development LT, Corporation I. CMOS Scaling for the 22nm Node and Beyond: Device Physics and Technology. 2011:1-2.

- 8. A.C. Diebold, A. Antonelli, and N. Keller, "Perspective: Optical measurement of feature dimensions and shapes by scatterometry," APL Mater. **6** (5), (2018).

- 9. D.F. Sunday and R.J. Kline, "Methodology for evaluating the information distribution in small angle scattering from periodic nanostructures", *J. Micro/Nanolithography, MEMS, and MOEMS* 17, (2018), 044002.

- 10. M. Korde, S. Kal, C. Pereira, S. Keller, A. Mosden, and A. Diebold,. "Optical characterization of multi-NST nanowire test structures using Mueller matrix spectroscopic ellipsometry (MMSE) based scatterometry for sub 5nm nodes," Proc. SPIE 10959 Metrology, Inspection, and Process Control for Microlithography XXXIII, 109590X (2019).

- M. Liehr, J. Hazra, K. Beckmann, W. Olin-Ammentorp, N. Cady, Ryan Weiss, S. Sayyaparaju, G. Rose, and J. Van Nostrand. 2019. Fabrication and Performance of Hybrid ReRAM-CMOS Circuit Elements for Dynamic Neural Networks. In Proceedings of the International Conference on Neuromorphic Systems (ICONS '19). ACM, New York, NY, USA, Article 6, 4 pages. DOI: https://doi.org/10.1145/3354265.3354271

- 12. J.C. Wong and S. Salahudding, Negative Capacitance Transistors, Proceedings of the IEEE , 107, (2019) pp 49-62.

- 13. V. Mukundan, K. Beckmann, K. Tapily, S. Consiglio, R. Clark, G. Leusink, **N. Cady**, A.C. Diebold. Structural Correlation of Ferroelectric Behavior in Mixed Hafnia-Zirconia High-k Dielectrics for FeRAM and NCFET Applications. (2019) *MRS Advances*. 4(9): 545–551. doi: 10.1557/adv.2019.148.

Proc. of SPIE Vol. 11325 1132502-7

- 14 H. Mertens, et. al., Gate-all-around MOSFETs based on vertically stacked horizontal Si nanowires in a replacement metal gate process on bulk Si substrates, 2016 IEEE Symposium on VLSI Technology.

- 15. N. Loubet, et. al., Stacked Nanosheet Gate-all-Around transistor to enable scaling beyond FinFet, 2017 IEEE Symposium on VLSI Technology.

- 16. M. Korde, S. Kal, C. Alix, N. Keller, G.A. Antonelli, A. Mosden, A.C. Diebold, Non-destructive characterization of nanoscale sub-surface features fabricated by selective etching of multi-layered nanowire test structures using Mueller matrix spectroscopic ellipsometry based scatterometry, submitted.

- 17. Role of Ge and Si substrates in higher-k tetragonal phase formation and interfacial properties in cyclical ALD-anneal Hf<sub>1-x</sub>Zr<sub>x</sub>O<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> thin film stacks, S. Dey, K. Tapily, S. Consiglio, R. D. Clark, C. S. Wajda, G. J. Leusink, A.R. Woll, and A.C. Diebold, J. Appl. Phys. 120, (2016), 125304.

- 18. Structural correlation of ferroelectric behavior in mixed hafnia-zirconia high-k dielectrics for FeRAM and NCFET applications, V. Mukundan, K. Beckmann, K. Tapily, S. Consiglio, R. Clark, G. Leusink, N. Cady, A.C. Diebold, MRS Advances (2019), pp 1-17. <a href="https://doi.org/10.1557/adv.2019.148">https://doi.org/10.1557/adv.2019.148</a>

- 19. K. Beckmann, J. Holt, W. Olin-Ammentorp, J. Van Nostrand, N.C. Cady. Impact of etch process on hafnium dioxide based nanoscale RRAM devices. (2016) ECS Transactions. 75(13): 93-99.

- 20. M. Liehr, J. Hazra, K. Beckmann, W. Olin-Ammentorp, N. Cady, R. Weiss, S. Sayyaparaju, G. Rose, J. Van Nostrand. (2019) Fabrication and Performance of Hybrid ReRAM-CMOS Circuit Elements for Dynamic Neural Networks. In Proceedings of the International Conference on Neuromorphic Systems (ICONS '19). Association for Computing Machinery. 6:1–4.

Proc. of SPIE Vol. 11325 1132502-8